www.afm-journal.de

# Novel Heterogeneous Integration Technology of III–V Layers and InGaAs FinFETs to Silicon

Xing Dai, Binh-Minh Nguyen, Yoontae Hwang, Cesare Soci, and Shadi A. Dayeh\*

Heterogeneous integration of III-V compound semiconductors to Si substrates is regarded as a necessary step for advancing high-speed electronics and hybrid optoelectronic systems for data processing and communications, and is extensively being pursued by the semiconductor industry. Here, an innovative fab-compatible, hybrid integration process of III-V materials to Si, namely InGaAs thin films to insulator-on-Si, is reported, and the first III-V FinFET devices on Si are demonstrated. Transfer of crystalline InGaAs layers with high quality to SiO2/Si is accomplished by the formation of a robust interfacial nickel-silicide (NiSi) bonding interface, marking the first report for using silicides in III-V hybrid integration technology. The performance of optimally fabricated InGaAs FinFETs on insulator on Si is systematically investigated for a broad range of channel lengths and Fin perimeters with excellent switching characteristics. This demonstrates a viable approach to large-scale hybrid integration of active III-V devices to mainstream Si CMOS technology, enabling low-power electronic and fully-integrated optoelectronic applications.

### 1. Introduction

In the past three decades, III–V compound semiconductor materials have been widely used in high-speed integrated circuits for communication systems, enabling life-changing applications such as cell phones, broadband wireless, satellite communications, space, radar, fiber optic communications, and radio telescopes.<sup>[1]</sup> Silicon transistors on the other hand have reduced in size by over a million times since their invention in the late '40s, thereby increasing density and functionality while simultaneously reducing chip power consumption and production costs; meanwhile, their operation speed increased by over a billion times thanks to excellent processing control and

X. Dai, Dr. B.-M. Nguyen, Dr. Y. Hwang, Prof. S. A. Dayeh Department of Electrical and Computer Engineering University of California San Diego 9500 Gilman Dr MC 0407, La Jolla, California 92093, USA

E-mail: sdayeh@ece.ucsd.edu X. Dai, Prof. C. Soci

Division of Physics and Applied Physics Nanyang Technological University 21 Nanyang Link, Singapore 637371

Dr. B.-M. Nguyen Center for Integrated Nanotechnologies Los Alamos National Laboratory, P.O.Box 1663 MC K771, Los Alamos, New Mexico 87545, USA

DOI: 10.1002/adfm.201400105

recent rich advancements in strain engi-

buffer layers thinner than 2 µm on 4° offcut (100) Si. [6] Using epitaxial necking or aspect ratio trapping, the thickness of these buffer layers can be considerably reduced as successfully demonstrated for GaAs, [7] and InP[8] among others. While these are tremendously significant advances, a defect-free III-V channel on Si using these approaches has not been currently achieved. On the other hand, hybrid integration with processes including Smart Cut,[9] and direct covalent wafer bonding based on oxide layers, [10] require extremely smooth surfaces (typical surface roughness of ≤0.5 nm per bonded surface), which overall results in a tight process and low yield. Other hybrid integration approaches utilize intermediate bonding layers such as eutectics,[11] and polymer layers,[12] where the former is not CMOS favored due to the low melting temperature (with usually non-Si-compatible Au composition) and the latter has poor thermal conduction and has limited thermal budget for postprocessing (e.g., post transfer metal alloy contact formation).

Recent advances in direct layer transfer upon epitaxial lift-off (ELO) of thin compound semiconductor films using sacrificial layers have shown enormous potential for large-scale integration of III-V on heterogeneous substrates for photovoltaic, [13] LED[13a] and FET[14] applications. Among the main advantages, research demonstrated that ELO and bonding allow large area transfer of various III–V crystalline compounds on Si, without limitations imposed by lattice mismatch constrains and without requiring complex processing steps. [13a,d,e] Here we develop a new approach to demonstrate a reliable III-V transfer process based on solid-state diffusion of Ni, deposited on a dielectric

ADVANCED FUNCTIONAL MATERIALS

www.afm-journal.de

layer that caps the III-V surface, into an exposed Si surface to form an interfacial NiSi bonding layer; further, we demonstrate that this method yields III-V bonded layers of high quality by fabricating high-performance InGaAs FinFET devices.

In the quest for higher density of integration, current CMOS transistor technology has evolved from planar device architectures to the so called FinFET geometry, which takes its name from the shape of the active channel resembling a vertical, three-dimensional Fin. The main benefit of this geometry is that the gate can be formed conformally around the three sides of the Fin (tri-gate) to achieve full control of the potential of the conducting channel. The multi-gate structure can effectively improve the transistor electrostatics in terms of lowering supply voltage and reducing short channel effects (SCE), which are widely observed in planar transistors where the source/ drain fields penetrate deep into the transistor channel under the gate reducing its effectiveness in controlling current flow and threshold voltage. Moreover, the FinFET architecture introduces fewer changes to conventional planar transistor design compared to surrounding gate transistors and multibridgechannel MOSFET, two of the other three-dimensional competing technologies.<sup>[15]</sup> Similar FinFET structures have also been adopted in high mobility III-V transistors, for instance made of InGaAs grown epitaxially on InP substrates with high-k gate dielectrics, which showed improvement of the short channel performance.[16]

#### 2. Results and Discussion

To exploit the advantages of FinFET transistors in a manufacturable platform, we combined our III-V transfer process based on NiSi bonding to realize, for the first time, InGaAs FinFET devices on Si with sub-20 nm channel width. This first batch of undoped InGaAs FinFETs showed excellent features in terms of low off-current, steep turn on characteristics, and immunity to SCE, which are comparable to those of well-developed III–V FinFETs on InP substrates. [16a,17] A key advantage of our fabrication workflow is that it's fully compatible with CMOS technology and could straightforwardly be deployed to allow

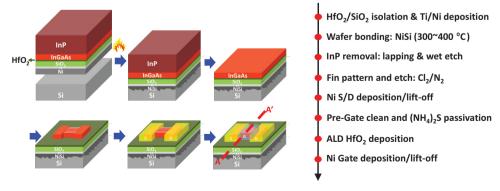

multiple substrate reuses. The heterogeneous integration technology and device fabrication process are schematically illustrated in Figure 1. The starting substrate comprises of an undoped InGaAs layer (50 nm) grown on bulk semi-insulating InP wafer. Dielectric stacks of HfO2 and SiO2 were then deposited, followed by the e-beam evaporated Ti/Ni metal layers. Our bonding scheme utilizes the NiSi interface alloyed at temperatures as low as 300 °C to fuse the InGaAs/InP wafer to a Si host substrate. Detailed transmission electron microscopy (TEM) and electrical characterization confirmed the formation of nickel monosilicide interfacial bonding layers.<sup>[18]</sup> For the purpose of demonstrating this new bonding approach, the bulk InP substrate was thinned by mechanical lapping and completely removed by HCl:H<sub>2</sub>O (3:1) wet etching. Note, however, that sacrificial layers such as thin AlAs/InAlP layers could be simply included in the initial heterostructures growth on the donor InP substrate to implement ELO and reuse of the InP substrate for subsequent epitaxial growths and transfers. [13a-c,19] Transfer yield of the process was greater than 90% even for the largest 2 cm  $\times$  2 cm InGaAs area we tested, where only the edges were found to be prone to exfoliation limited by edge effects on the cut 2 cm  $\times$  2 cm samples.

After transferring the InGaAs layers onto the Si substrate, device fabrication of advanced III-V electronic and optoelectronic devices becomes feasible which is demonstrated here for the case of the first InGaAs FinFETs on Si. The 3D device fabrication proceeded by defining arrays of 5 or 10 parallel InGaAs "Fins" by electron-beam lithography and a Cl<sub>2</sub>/N<sub>2</sub> inductively coupled plasma etching of the InGaAs Fins. After the InGaAs dry etch, a cyclic O2 plasma, dilute buffer oxide etch (BOE) and deionized water cleaning were performed to remove the e-beam resist and etch mask (see experimental methods) and reduce the surface roughness of the InGaAs Fins. During this process, the height of the Fins is reduced from that of the original InGaAs layer thickness of 50 nm to ≈35 nm. These devices feature Ni S/D contact region, a 5 nm HfO2 gate dielectric deposited by atomic layer deposition (ALD) with an equivalent oxide thickness (EOT, the thickness of an SiO2 layer that would result in the same capacitance as the high-k material) of 1.11 nm, and an accurately aligned Ni gate electrode. State of the art wet

**Figure 1.** Schematic illustration of the NiSi III-V to Si wafer bonding and fabrication process flow of an undoped  $In_{0.53}Ga_{0.47}As$  channel FinFETs on Si. Atomic Layer Deposited (ALD)  $HfO_2$  (15 nm) followed by plasma enhanced chemical vapor deposition (PECVD)  $SiO_2$  layers (200 nm) were deposited on InGaAs for isolation and as a barrier for Ni diffusion. A Ti/Ni (15/100 nm) stack is e-beam evaporated on top, and the whole structure was brought in contact with Si and annealed at 400 °C to form a NiSi bonding interface. The InP substrate was removed, leaving then an InGaAs layer on insulator on Si that was then etched into Fin structures. After S/D Ni deposition and lift-off, pre-gate wet and in-situ plasma surface treatments followed and 5 nm ALD  $HfO_2$  was deposited. Ni metal gates were finally deposited and lifted-off.

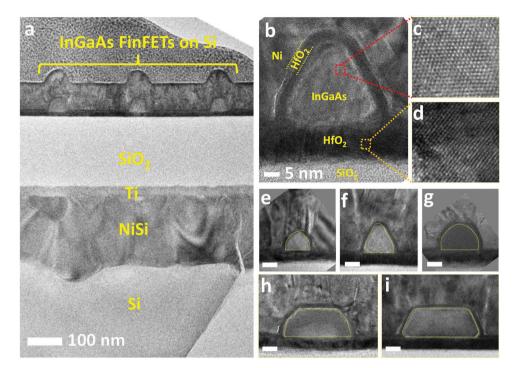

Figure 2. a) Cross-sectional TEM image of three fabricated InGaAs FinFETs with gate dielectric and tri-gate atop showing the whole structure of the devices on Si (Figure 1 A-A'). The white contrast feature in the NiSi layer at the right side of the image is a crack at the edge of the thinned cross-section. b) HRTEM of a completed single InGaAs FinFET showing conformal amorphous 5 nm HfO2 gate dielectric on the edges of the InGaAs Fin (top width is 13 nm, left sidewall height is 36 nm, and right sidewall height is 36 nm) with a Ni gate atop. Zoom-in images in (c,d) illustrate the preserved single crystal InGaAs channel after bonding and bottom crystallized HfO2 that was formed during NiSi reaction, respectively. Panels (e-i) depict the crosssectional TEM images of FinFETs with various three side perimeters of 60 nm, 85 nm, 100 nm, 130 nm and 150 nm. Scale bar for panels (e-i) is 20 nm.

chemical treatments and in-situ ALD plasma treatments with extensive and systematic capacitance-voltage characterization of metal-insulator-InAs/InGaAs structures were conducted to reduce the leakage current and improve the interface quality (Experimental Section and Supporting Information, procedure and Figures S1-S7). The resulting devices consisted in arrays of InGaAs FinFETs with 5 or 10 parallel Fins with channel length  $L_{\rm ch}$  varying from 35 nm to 950 nm.

Illustrated in Figure 2a is the cross-sectional TEM image (along A-A' cut in Figure 1) of the whole structure of three finished InGaAs FinFET devices on a stack of HfO2/SiO2/NiSi/ Si. Due to the formation of NiSi (≈4.7% lattice mismatched to Si), the NiSi layer contains multiple grains and stacking faults, the presence of which is unavoidable but does not compromise the integrity of the III-V layers atop, or possible CMOS devices in the vicinity. It is important to note that no defective regions have been identified by TEM in the Si sample itself after the NiSi bonding procedure. The (001) Si/NiSi interface is typically non-flat and can become smooth and flat with the use of (111) surfaces and thin Ni layers. Figure 2b depicts a high resolution TEM (HRTEM) image of a tri-gated InGaAs FinFET (13 nm top width and 36 nm slanted sidewall lengths) retaining single crystal quality (Figure 2c) with 5 nm conformally covered HfO<sub>2</sub> gate dielectric on the Fin top and sidewalls. The bottom HfO<sub>2</sub> layer is used as a post-anneal HF-etch stop layer in our process and displays a polycrystalline structure (Figure 2d) due to NiSi high temperature bonding process. The HfO2 crystallization led to electrical shorts in devices made without SiO2 layers where

current paths between the FET device leads on top and through the HfO2 to the NiSi layer and then to the electrode leads were created. The leakage through HfO2 necessitated an insertion of a SiO2 layer underneath it for electrical isolation from the underlying NiSi layer. Cross-sectional TEM images of five final FinFET devices in Figure 2e-i demonstrate FinFET perimeter variation of 60 nm, 85 nm, 100 nm, 130 nm and 150 nm with slanted sidewalls due to erosion of the etching mask during the plasma etch.

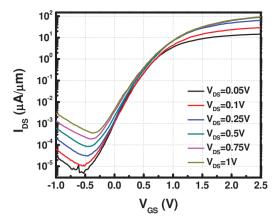

Transistor performance of all devices was measured after 5 min rapid thermal annealing at 200 °C in forming gas (H<sub>2</sub>/N<sub>2</sub> mixture) ambient. The transfer characteristics of a representative device with 10 InGaAs FinFET channels with  $L_{ch} = 390$  nm, P = 60 nm are shown in **Figure 3**, where the current is normalized by the perimeter of the Fins, measured by TEM, and by the number of channels. This device exhibited an  $I_{\rm on}$  = 18  $\mu$ A  $\mu$ m<sup>-1</sup> at  $V_{\rm DS} = 0.5$  V and  $V_{\rm GS} - V_{\rm T} = 0.5$  V, where the threshold voltage  $V_T = 0.78$  V was extracted by the linear extrapolation of the  $I_{\rm DS}-V_{\rm GS}$  at the maximum slope (peak transconductance,  $g_{\rm m}$ ). [20] The on-current of these devices was limited by the series contact resistance due to the Schottky barrier nature between the Ni S/D contacts and the undoped InGaAs, which was also responsible for the increment of  $I_{DS}$  in the negative  $V_{GS}$  region from hole transport. [21] An inverse subthreshold slope (SS-1) of 165 mV dec<sup>-1</sup> and a maximum current sweep ratio ( $I_{\text{max}}/I_{\text{low}}$ ) of 3.2  $\times$   $10^6$  at  $V_{\rm DS}$  = 0.05 V were observed. The interface quality for these FinFET devices on Si compares well to those on InP<sup>[22]</sup> and lags behind some others with Al<sub>2</sub>O<sub>3</sub> interfacial

ADVANCED FUNCTIONAL MATERIALS

www.afm-journal.de

**Figure 3.** Measured transfer characteristics of an InGaAs FinFET on Si with P=60 nm and  $L_{\rm ch}=390$  nm for different  $V_{\rm DS}$  biases showing the highest  $I_{\rm max}/I_{\rm low}$  of  $3.2\times10^6$  and SS<sup>-1</sup> of 165 mV dec<sup>-1</sup> at  $V_{\rm DS}=0.05$  V.

gate dielectric layers. [16b] Further optimization of the HfO<sub>2</sub>/InGaAs interface and reduced Fin widths would result in lower SS<sup>-1</sup>. The gate leakage was as low as  $10^{-6} \, \mu\text{A}/\mu\text{m}$  for all the  $V_{\text{DS}}$  biases used in this study up to  $V_{\text{DS}}=1$  V.

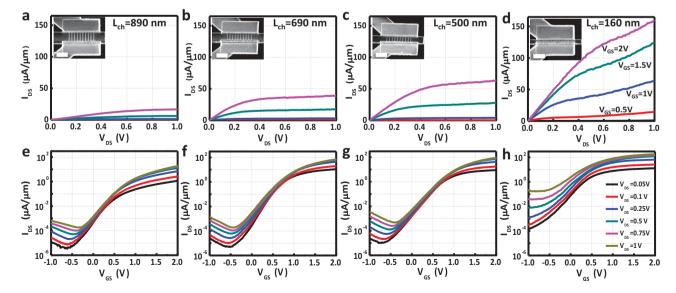

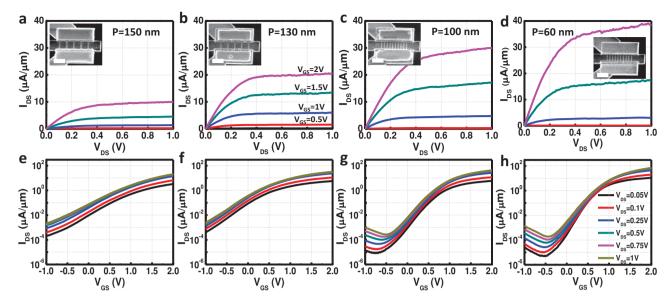

**Figure 4** compares the normalized output and transfer curves for devices with the same perimeter of P=60 nm and with various channel lengths of  $L_{\rm ch}=890$  nm, 690 nm, 500 nm, and 160 nm. Shorter channel length devices exhibited higher drive currents (Figure 4d), more severe SCE, larger off currents and worse SS<sup>-1</sup> (Figure 4h), whereas the on-state performance did not scale linearly with  $L_{\rm ch}$  due to the large S/D contact resistance for these undoped InGaAs devices. With decreasing Fin perimeter for the same channel length ( $L_{\rm ch}=690$  nm),  $I_{\rm DS}$  enhancement was observed as shown in **Figure 5**a–d. Such enhancement has been attributed to increased quantum confinement and increased carrier mobility resulting from reduced

interface scattering.<sup>[23]</sup> In addition, the transfer curves indicated an improved SS<sup>-1</sup> and on/off characteristics with decreasing perimeter as shown in Figure 5e–h.

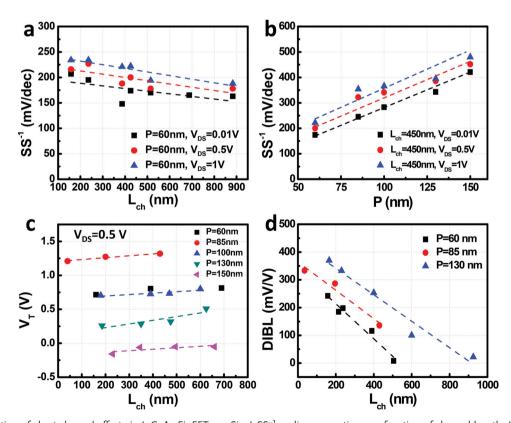

The scaling metrics for InGaAs FinFETs on insulator-on-Si with various gate lengths and Fin widths are summarized in Figure 6, including  $SS^{-1}$ , threshold voltage,  $V_T$ , and drain induced barrier lowering, DIBL (resulting in  $V_T$  reduction with a  $V_{DS}$  increase in transistors with short channel lengths). Figure 6a shows that  $SS^{-1}$  was degraded for all  $V_{DS}$  values with reducing  $L_{\rm ch}$  from 900 nm to 150 nm, and a higher SS<sup>-1</sup> was observed for higher  $V_{DS}$ , as expected, due to SCE (Figure 6a). The lowest SS<sup>-1</sup> of 150 mV dec<sup>-1</sup> was obtained at  $V_{DS} = 0.01 \text{ V}$ for the device with  $L_{\rm ch}=390~{\rm nm}$  and  $P=60~{\rm nm}$ . For a variable perimeter with same  $L_{ch} = 450$  nm depicted in Figure 6b, SS<sup>-1</sup> improved dramatically from 420 mV dec-1 to 160 mV dec-1 with decreasing perimeter from 150 nm to 60 nm at  $V_{DS}$  = 0.01 V. Channel length scaling that is immune to SCE can be achieved by narrowing the Fin width. Figure 6c exhibits the influence of  $L_{\rm ch}$  (35 nm to 700 nm) and perimeter (60 nm to 150 nm) change on  $V_T$ , where  $V_T$  was obtained by the linear extrapolation method discussed above at  $V_{\rm DS} = 0.5$  V. A slight increase of  $V_T$  with  $L_{ch}$  was observed for all perimeters from 60 nm to 150 nm, but  $V_T$  was found to increase dramatically with decreasing perimeter, pulling the device into a desired enhancement mode operation. With  $L_{\rm ch}$  of  $\approx$ 400 nm, and as P increases from 85 nm to 150 nm, a negative shift in  $V_{\rm T}$ of 1.4 V was required to deplete the channel. This trend was confirmed for perimeters of P = 85 nm, 100 nm, 130 nm, and 150 nm, and Silvaco Atlas 3D simulations provided supporting evidence for this 'body-thickness' effect (Figure S8, Supporting Information). For P = 60 nm,  $V_T$  was found to be close to that of P = 100 nm, both of which had a circular cross-sectional perimeter at the top portion of the Fin, compared to all other Fins. However, process variations cannot be excluded to interpret this surprising similarity in  $V_T$ . Figure 6d shows that the

Figure 4. Influence of channel length ( $L_{ch}$ ) on device performance for a fixed perimeter, P=60 nm. Illustrated are a–d) output and e–h) transfer characteristics. The output characteristics ( $V_{GS}$  is varied from 0 to 2 V in steps of 0.5 V) exhibited an increasing current accompanied with an increased output conductance in the saturation regime for shorter channel lengths. The transfer characteristics were degraded with shorter channel lengths. Scale bars of all inset SEM images are 1  $\mu$ m.

Figure 5. Influence of FinFET perimeter (P) on device performance for a fixed channel length,  $L_{ch} = 690$  nm. Illustrated are a–d) the output and e–f) transfer characteristics for devices with P = 150 nm, 130 nm, 100 nm, and 60 nm. e–h) Larger on-currents and better transfer properties are measured for smaller perimeters. Scale bars of all inset SEM images are 1  $\mu$ m.

DIBL increased with shorter  $L_{\rm ch}$  due to SCE but this effect was suppressed for smaller P. The DIBL degrades from 8 mV/V to 410 mV/V when  $L_{\rm ch}$  was reduced from 925 nm to 180 nm for a

fixed P of 130 nm. On the other hand, when P was decreased from 130 nm to 60 nm with a fixed  $L_{\rm ch}$  of 400 nm, DIBL decreased from 265 mV/V to 115 mV/V. These metrics indicate

**Figure 6.** Evaluation of short channel effects in InGaAs FinFETs on Si. a) SS<sup>-1</sup> scaling properties as a function of channel length,  $L_{\rm ch}$ , for P=60 nm and for different  $V_{\rm DS}$  biases. b) SS<sup>-1</sup> scaling properties as a function of perimeter P for a fixed  $L_{\rm ch}=450$  nm and for different  $V_{\rm DS}$  biases. c) Scaling properties of the threshold voltage,  $V_{\rm T}$ , as a function of  $L_{\rm ch}$  and for different P demonstrating a stronger effect of the P on  $V_{\rm T}$  with relatively insignificant change with  $L_{\rm ch}$  for the same P. d) DIBL scaling properties as a function of  $L_{\rm ch}$  down to 35 nm and with various P.

ADVANCED FUNCTIONAL MATERIALS

www.MaterialsViews.com

www.afm-journal.de

that devices with longer  $L_{\rm ch}$  and smaller P will have improved SS<sup>-1</sup>, DIBL, and  $I_{\rm on}/I_{\rm off}$  without suffering much from SCE. More sophisticated processing, including retrograde channel doping,<sup>[22]</sup> decreasing EOT<sup>[24]</sup> (Supporting Information), gate first, self-aligned S/D<sup>[21a]</sup> and utilizing gate all around 3D structure,<sup>[16b]</sup> could help in improving the gate control of the channel and further suppressing the SCE.

#### 3. Conclusion

We demonstrated a novel heterogeneous integration technology for thin III–V layers to Si by NiSi formation for advanced active electronic and optoelectronic III-V devices on Si. We reported the fabrication of the first InGaAs FinFETs on insulator on Si by such fab-compatible process using this new integration platform, and systematically investigated the scaling metrics of InGaAs FinFETs with high-k dielectric and metal gate and provided insights into improving their performance. This demonstration highlights the potential of high performance InGaAs FinFETs on Si for ultimately scaled III-V logic technology, and paves the way for incorporating a variety of III-V electronic and optoelectronic devices on a Si CMOS platform.

## 4. Experimental Section

Wafer Bonding: The undoped 50 nm thick InGaAs was grown on semiinsulating InP (001) substrate by molecular beam epitaxy at Intellginet Epitaxy Inc. In preparation for wafer bonding, the native oxide layer on the surface of the InGaAs was removed by a diluted BOE. An HfO2 layer (15 nm) was deposited by atomic layer deposition (H2O source kept at 20 °C and Tetrakis (dimethylamino) hafnium (TDMAH) source kept at 75 °C) atop the InGaAs/InP sample at 200 °C, followed by a SiO2 dielectric layer (200 nm) deposition by plasma enhanced chemical vapor deposition for electrical isolation. A Ti adhesion layer (15 nm) followed by a Ni "bonding" layer (100 nm) were deposited by e-beam evaporation. This material stack ( $Ni/Ti/SiO_2/HfO_2/InGaAs/InP$ ) was then brought in contact with a Si sample with similar area (typically 1 cm  $\times$  1 cm) that was cleand by "Piranha" solution (H2SO4:H2O2 3:1) and HF. 400 °C rapid thermal annealing in forming gas ambient (N2:H2 85%:15%) for 10 mins was then performed on this stack with pressure applied on both sides by a silver metal paperclip, which led to the formation of a bonding NiSi interface between the III-V stack and Si.

InGaAs FinFET Fabrication: After bonding of the III-V stack to Si, the InP wafer was thinned down by mechanical lapping on a polishing cloth to a thickness of  $\approx$ 70–100  $\mu m$  which was then selectively etched by HCl:H2O (3:1) leaving the 50 nm InGaAs atop HfO2/SiO2/NiSi/Ti/ Si. The device fabrication utilized a 100 KeV electron-beam lithography (JEOL JBX-6300FS) system to pattern arrays of 5 or 10 parallel InGaAs "Fins" with widths ranging from 20 to 200 nm. Negative electron beam resist Hydrogen Silsesquioxane (HSQ, XR-1541-004), was used as the etch mask for the Cl<sub>2</sub>/N<sub>2</sub> inductively coupled plasma/reactive ion etching of the InGaAs Fins. After the InGaAs Fin etch, a cyclic O2 plasma, and dilute BOE (BOE:H2O 1:10 volume ratio) cleaning was performed to remove the HSQ etch mask and reduce the surface roughness of the InGaAs Fins, whose height was also reduced to 35 nm. S/D contact regions were then patterned, followed by a BOE dip, and transferred immediately to an e-beam evaporator system for Ni deposition followed by lift-off. The native oxide of the InGaAs Fins was etched in diluted BOE, rinsed in deionized water, followed by 10 min 10% (NH<sub>4</sub>)<sub>2</sub>S dip for surface passivation.  $^{[25]}$  A 5 nm thick  $HfO_2$  layer was then deposited by ALD at 200 °C and were characterized versus different deposition and surface treatment parameters to provide the best interface quality (Supporting information). Overlapping gate electrodes were finally aligned and patterned by electron beam lithography, followed by Ni metal deposition. The resulting devices consisted in arrays of InGaAs FinFETs with 5 or 10 parallel channels with channel length  $L_{\rm ch}$  varying from 35 nm to 950 nm. The sample fabrication and morphology were characterized by an FEI SEM.

Transmission Electron Microscopy: The cross-sectional TEM samples were prepared using an FEI Nova 600 Nanolab dual beam system, consisting of SEM and focused ion beam (FIB). Pt was in-situ deposited along the targeting lamellae for sample surface protection purposes. Ion beam (gallium) was utilized to cut two trenches from each side, followed by mounting the sample on the nanomanipulator needle by Pt deposition. The sample was then lifted out and mounted on a TEM grid after a "U" cut on the cross-section. Fine cleaning further thinned down and polished the lamella in to an electron transparent thickness. HRTEM characterization was conducted in a 300 keV FEI Tecnai F30 system.

Electrical Characterization: Current-voltage (I–V) and capacitance voltage (C–V) characteristics were measured by an Agilent B1500A semiconductor parameter analyzer in fast scan mode. No significant influence of the integration time on the IV characteristics was observed.

## **Supporting Information**

Supporting Information is available from the Wiley Online Library or from the author.

## **Acknowledgements**

The authors are grateful to Dr. John Nogan and Mrs. Denise Webb of Sandia National Laboratories for their assistance with facility operation and useful discussions and for the insightful comments from Prof. S.S. Lau at UC San Diego. This work was performed, in part, at the Center for Integrated Nanotechnologies, an Office of Science User Facility operated for the U.S. Department of Energy (DOE) Office of Science. Los Alamos National Laboratory, an affirmative action equal opportunity employer, is operated by Los Alamos National Security, LLC, for the National Nuclear Security Administration of the U.S. Department of Energy under contract DE-AC52-06NA25396. X.D., B.M.N, Y.H., and S.A.D. acknowledge support from a faculty start-up fund at UC San Diego (ECER117) and Laboratory Directed Research and Development (LDRD) program at Los Alamos National Laboratory project numbers (20120747PRD1, 20100601PRD2), and partial support from the National Science Foundation, Division of Materials Research, DMR-Award No. 0902277. X.D. and C.S. acknowledge support from NTU-NAP start-up grant (M4080511).

Received: January 12, 2014 Revised: March 4, 2014 Published online: April 7, 2014

- [4] D. Hisamoto, W.-c. Lee, J. Kedzierski, H. Takeuchi, K. Asano, C. Kuo, E. Anderson, T.-j. King, J. Bokor, C. Hu, *IEEE Trans. Electron Devices* 2000, 47, 2320.

- [5] a) J. A. del Alamo, *Nature* 2011, 479, 317; b) International Technology Roadmap For Semiconductors (ITRS) 2011 Edition Excecutive Summary Page 38.

- [6] N. Mukherjee, J. Boardman, B. Chu-Kung, G. Dewey, A. Eisenbach, J. Fastenau, J. Kavalieros, W. K. Liu, D. Lubyshev, M. Metz,

J. A. del Alamo, Int. Conf. Compd. Semicond. Manufact. Technol. 2011, 17.

<sup>[2]</sup> J. Welser, J. L. Hoyt, S. Takagi, J. F. Gibbons, Int. Electron Devices Meeting, Technical Digest 1994, 373.

<sup>[3]</sup> G. D. Wilk, R. M. Wallace, J. M. Anthony, J. Appl. Phys. 2001, 89, 5243.

www.afm-iournal.de

www.MaterialsViews.com

- K. Millard, M. Radosavljevic, T. Stewart, H. W. Then, P. Tolchinsky, R. Chau, Int. Electron Devices Meeting 2011, 35.1.1

- [7] J. Z. Li, J. Bai, J. S. Park, B. Adekore, K. Fox, M. Carroll, A. Lochtefeld, Z. Shellenbarger, Appl. Phys. Lett. 2007, 91, 021114.

- [8] J. Z. Li, J. Bai, J. M. Hydrick, J. G. Fiorenza, C. Major, M. Carroll, Z. Shellenbarger, A. Lochtefeld, ECS Trans. 2009, 18, 887.

- [9] a) M. Bruel, Electron. Lett. 1995, 31, 1201; b) L. Czornomaz, N. Daix, D. Caimi, M. Sousa, R. Erni, M. D. Rossell, M. El-Kazzi, C. Rossel, C. Marchiori, E. Uccelli, M. Richter, H. Siegwart, J. Fompeyrine, Int. Electron Devices Meeting 2012, 23.4.1.

- [10] a) D. Liang, A. W. Fang, H. Park, T. E. Reynolds, K. Warner, D. C. Oakley, J. E. Bowers, J. Electron. Mater. 2008, 37, 1552; b) M. Yokoyama, R. Iida, Y. Ikku, S. Kim, H. Takagi, T. Yasuda, H. Yamada, O. Ichikawa, N. Fukuhara, M. Hata, M. Takenaka, S. Takagi, Semicond. Sci. Technol. 2013, 28, 094009; c) S. A. Dayeh, P. Chen, Y. Jing, E. T. Yu, S. S. Lau, D. Wang, Appl. Phys. Lett. 2008, 93, 203109.

- [11] G. S. Matijasevic, C. C. Lee, C. Y. Wang, Thin Solid Films 1993, 223,

- [12] W. Chen, P. Chen, J. E. Pulsifer, T. L. Alford, T. F. Kuech, S. S. Lau, Appl. Phys. Lett. 2008, 92, 212109.

- [13] a) C. W. Cheng, K. T. Shiu, N. Li, S. J. Han, L. Shi, D. K. Sadana, Nat Commun 2013, 4, 1577; b) A. Polman, H. A. Atwater, Nat. Mater. 2012, 11, 174; c) G. J. Bauhuis, P. Mulder, E. J. Haverkamp, J. C. C. M. Huijben, J. J. Schermer, Sol. Energy Mater. Sol. Cells 2009, 93, 1488; d) R. Tatavarti, G. Hillier, A. Dzankovic, G. Martin, F. Tuminello, R. Navaratnarajah, G. Du, D. P. Vu, N. Pan, IEEE Photovoltaic Specialists Conf. 2008, 1; e) A. Cornfeld, D. Mcglynn, T. Varghese, US 20100047959A1 2010.

- [14] H. Ko, K. Takei, R. Kapadia, S. Chuang, H. Fang, P. W. Leu, K. Ganapathi, E. Plis, H. S. Kim, S. Y. Chen, M. Madsen, A. C. Ford, Y. L. Chueh, S. Krishna, S. Salahuddin, A. Javey, Nature 2010, 468, 286.

- [15] a) D. Hisamoto, T. Kaga, Y. Kawamoto, E. Takeda, Int. Electron Devices Meeting. 1989, 833; b) X. Huang, W.-C. Lee, C. Kuo, D. Hisamoto, L. Chang, J. Kedzierski, E. Anderson, H. Takeuchi,

- Y.-K. Choi, K. Asano, V. Subramanian, T.-J. King, J. Bokor, C. Hu, Int. Electron Devices Meeting 1999, 67; c) C. Auth, C. Allen, A. Blattner, D. Bergstrom, M. Brazier, M. Bost, M. Buehler, V. Chikarmane, T. Ghani, T. G. Glassman, R. Han, W. Hanken, D. Hattendorf, M. Hentges, P. Heussner, R. Hicks, J. Ingerly, D. Jain, P. Jaloviar, S. James, R. Jones, D. Jopling, J. Joshi, S. Kenyon, C. Liu, H. McFadden, R. Mcintyre, B. Neirynck, J. Parker, C. Pipes, L. Post, I. Pradhan, S. Prince, M. Ramey, S. Reynolds, T. Roesler, J. Sandford, J. Seiple, J. Smith, P. Thomas, C. Towner, D. Troeger, T. Weber, C. Yashar, P. Zawadzki, K. Mistry, Symp. VLSI Technol. 2012, 131.

- [16] a) F. Xue, A. Jiang, Y.-T. Chen, Y. Wang, F. Zhou, Y.-F. Chang, J. Lee, Int. Electron Devices Meeting 2012, 27.5.1; b) J. J. Gu, X. W. Wang, H. Wu, J. Shao, A. T. Neal, M. J. Manfra, R. G. Gordon, P. D. Ye, Int. Electron Devices Meeting 2012, 27.6.1.

- [17] a) J. J. Gu, P. D. Ye, ECS Trans. 2012, 45, 217; b) X. Zhang, H. X. Guo, Z. Zhu, X. Gong, Y.-C. Yeo, Solid-State Electron. 2013, 84, 83.

- [18] S. A. Dayeh, W. Tang, B.-M. Nguyen, X. Dai, Y. Liu, Y. Hwang, X.-H. Liu, R. Chen, ECS Trans. 2013, 58, 115.

- [19] K. Lee, K.-T. Shiu, J. D. Zimmerman, C. K. Renshaw, S. R. Forrest, Appl. Phys. Lett. 2010, 97, 101107.

- [20] Y. Taur, T. H. Ning, Fundamental of Modern VLSI Devices, Cambridge University, Cambridge, 1998, 138.

- [21] a) X. Zhang, Ivana, H. X. Guo, X. Gong, Q. Zhou, Y.-C. Yeo, J. Electrochem. Soc. 2012, 159, H511; b) W. Lu, P. Xie, C. M. Lieber, IEEE Trans. Electron Devices 2008, 55, 2859.

- [22] H.-C. Chin, X. Gong, L. Wang, H. K. Lee, L. Shi, Y.-C. Yeo, IEEE Electron Device Lett. 2011, 32, 146.

- [23] J. J. Gu, H. Wu, Y. Liu, A. T. Neal, R. G. Gordon, P. D. Ye, IEEE Electron Device Lett. 2012, 33, 967.

- [24] Y. Wu, P. D. Ye, ECS Trans. 2010, 28, 185.

- [25] E. O'Connor, B. Brennan, V. Djara, K. Cherkaoui, S. Monaghan, S. B. Newcomb, R. Contreras, M. Milojevic, G. Hughes, M. E. Pemble, R. M. Wallace, P. K. Hurley, J. Appl. Phys. 2011, 109, 024101.